Hoe maak je een eenvoudige seriële UART-zender in verilog HDL

De meeste Universal Asynchronous Receiver Transmitter (UART) die ik online heb gevonden, zijn te ingewikkeld en moeilijk te begrijpen, hier zal ik een eenvoudige theorie uitleggen en ook code over hoe je er een kunt bouwen.

Laten we eerst praten over hoe zenders werken. Het basisprincipe is om meerdere databits over een enkele lijn te verzenden. In onze zender zijn deze gegevens parallel, maar om het aantal benodigde draden te verminderen, gebruiken we seriële communicatie die aan de ontvangende kant wordt omgezet naar parallel.

De basis dingen die we nodig hebben zijn de volgende:

- Een klokverdeler (onze teller)

Dit stelt ons in staat om gegevens met een bepaalde snelheid (baudrate) te verzenden. Onze ontvanger zal de gegevens beetje bij beetje bemonsteren en opnemen.

- Een schuifregister

We moeten weten hoeveel bits we tegelijk verzenden, ons schuifregister heeft een startbit, databits, pariteitsbit (optioneel), eindbit.

- Een toestandsdiagram

Voordat we code schrijven, moeten we bedenken wat we moeten maken en de beste manier is om een statusdiagram van ons ontwerp te maken. We weten dat we voor een zender 2 toestanden nodig hebben, IDLE en TRANSMITTING.

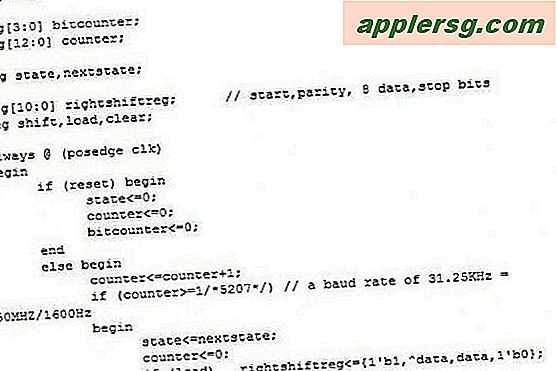

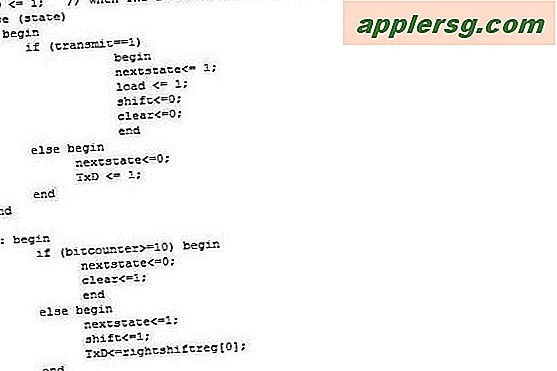

Nadat we een toestandsdiagram hebben, kunnen we nu berekenen wat onze teller zal zijn. Dit wordt gedaan door gebruik te maken van:

teller = FPGA-kloksnelheid/ baudrate

In dit voorbeeld gebruik ik een baudrate van 9600, waardoor mijn teller = 5208.

Als laatste berekenen we ons ploegenregister en voltooien we het schrijven van onze toestandsmachine. In mijn voorbeeldcode gebruik ik een startbit, pariteitsbit, 8 bits gegevens en eindbit. Dit is in totaal 11 bits.

Beide afbeeldingen in stap 2 en 3 samen in dezelfde module completeren onze zendercode die nodig is om naar de FPGA te programmeren. Deze code werkt met een andere FPGA die serieel is aangesloten of met Windows Hyperterminal naast andere hardware. Kan gemakkelijk worden aangepast om met veel meer te werken.

Als laatste maken we een testopstelling om eventuele fouten op te lossen en ons programma te simuleren voordat we de FPGA programmeren.

Dit concludeert de zender. Laat alsjeblieft een reactie achter als je vragen hebt of als je het gevoel hebt dat er hier iets ontbreekt.

Tips

Zowel zender als ontvanger moeten de baudrate weten waarmee gegevens worden verzonden.